Ripple Carry Adder:您需要知道的一切

- 发表时间:2021-10-12 09:50:53

- 来源:本站

- 人气:1347

逻辑电路可以依靠纹波进位加法器将 n 位值加在一起。因此,这种数字电路实现在许多应用中提供了有用的功能。然而,由于计算过程缓慢,它也表现出延迟的性能。这通常涉及等待每个全加器级将位纹波到下一个全加器级。这样的过程不断重复,直到结束,提供结果。

理解纹波进位加法器似乎有点令人困惑。考虑到这一点,我们将这篇文章放在一起,以帮助您获得有关此主题的更多知识。让我们开始吧!

什么是波纹进位加法器?

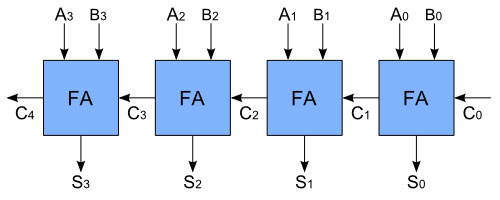

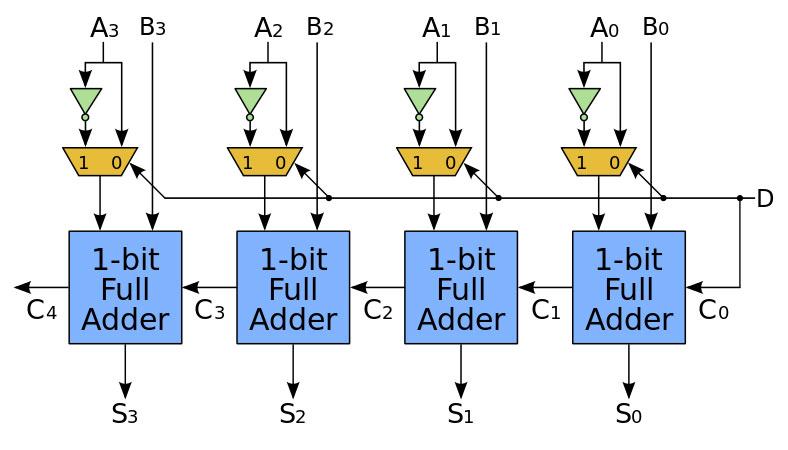

纹波进位加法器用作数字电路,将两个二进制 n 位数字相加并提供结果。它的结构由几个全加器组成,每个全加器以级联设置连接。以这种方式,全加器的进位输出连接到下一个全加器输入。

4 位纹波携带加法器的示意图。

资料来源:维基共享资源

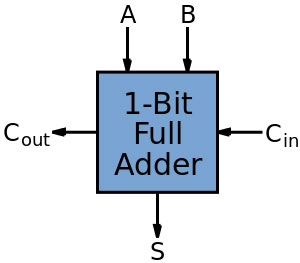

全加器代表一个逻辑电路,旨在将三个输入相加,同时生成两个输出。更具体地说,两个输入用作 A 和 B,而第三个输入表示一个进位位。(C-IN) 同时,一个输出代表进位输出位(C-OUT),另一个代表求和位(S)。最终,全加器电路可以连接到八个输入以形成一个字节宽的加法器。这将一个进位位从一个加法器级联到下一个。将两个半加器电路连接在一起将形成一个全加器。

一个完整的加法器逻辑图

资料来源:维基共享资源

纹波进位加法器工作原理

每个进位通过一个全加器级生成,然后通过其输入进入下一个全加器。整个过程继续进行,直到到达最终的全加器。结果,每个进位输出位波纹到下一个全加器级。总的来说,最关键的操作是将每个输入位序列加在一起,例如 4 位加法器、8 位加法器、16 位加法器等。

由于逻辑电路的传播延迟,在进位阶段结束之前,总和和进位位保持无效。由于输入和输出之间经过的时间量,通常会发生传播延迟。例如,当非门输入设置为 0 时,输出将配置为 1,等等。传播延迟定义了输出设置为零和输入配置为 1 之间经过的时间。此外,进位传播延迟定义了接收进位信号和执行进位信号之间经过的时间。

波纹进位加法器真值表

的真值表,如下所示,确定用于在一个脉动进位加法器的所有输入中的每个输出值。

涟漪带有加法器真值表。

波纹进位加法器 VHDL 代码和 Verilog 代码

要实现纹波进位加法器,您将需要VHDL 代码和 Verilog 代码。提供了两个示例。第一个涉及两位纹波进位加法器。同时,另一个示例产生一个纹波进位加法器,它收集每个输入宽度作为参数。

纹波进位加法器应用

时钟包含一个纹波进位加法器

对两个 N 位值执行加法

数字信号处理和微处理器

计时器

计算器

时钟

Ripple Carries Adder的优缺点

好处

纹波进位加法器并不昂贵。

资料来源:维基共享资源

通过 n 位加法提供准确的结果

简单的设计和开发过程

物美价廉

缺点

延迟会对其整体功能造成不便

它一次只允许一个全加器运行

进位延迟导致它运行缓慢

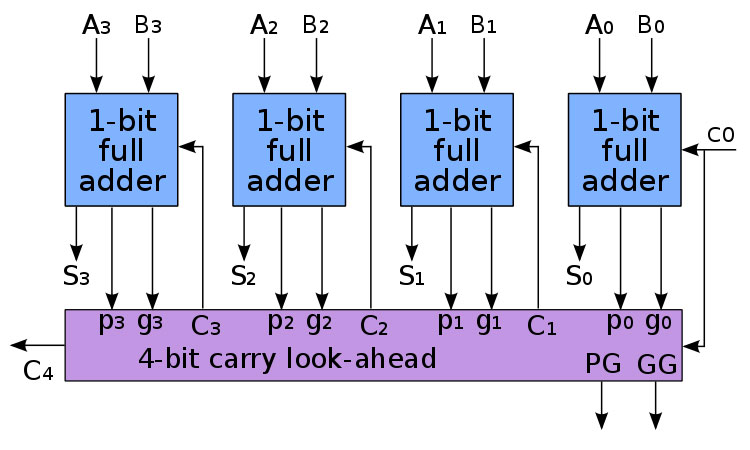

进位前瞻加法器

进位超前逻辑在达到总和之前计算进位位,有效地减少了时间延迟。这发生在通过两种方法生成进位信号之后。第一个涉及等于 1 的 a 和 b 位。同时,第二种方法涉及进位和等于 1 的 a 或 b 位。这些位在前一级实现,而进位在加法器的开头开始。

进位前瞻加法器原理图。

资料来源:维基共享资源

在纹波进位加法器中,每个全加器在计算总和之前将进位位处理到下一个加法器。因此,该过程会导致很长的延迟。

概括

总的来说,进位纹波加法器提供了在数字电路中将两个 n 位数字相加的能力。尽管过程缓慢,但它仍然具有有用的应用程序,这些应用程序本质上有助于数字信号处理。以这种方式,纹波进位加法器将进位位纹波到每个全加器级,直到它到达最后的全加器。此时,它将执行所需的计算。但是,进位超前加法器可以更快地完成此计算,因为它使用了不同的技术。从而减少延迟时间。

您对纹波进位加法器有任何疑问吗?请随时与我们联系!

【上一篇:】Ir Blaster:如何理解和使用IR Blaster

【下一篇:】铅酸电池充电器电路-不同的充电策略

- 2025-02-20深圳SMT贴片加工如何计算报价?

- 2026-04-022026年小家电行业在PCBA代工代料中应用自动化光学检测(AOI)的最新行业标准是什么?

- 2026-04-01代工代料模式下,智能家居产品的高频高速信号完整性测试规范包含哪些核心指标?

- 2026-03-26深圳周边一站式PCBA代工代料厂家推荐:高效率与质量的优选方案

- 2026-03-17PCBA代工代料与来料加工,哪种模式综合成本更低?求真实对比

- 2026-03-16医疗级PCBA代工代料,如何满足ISO13485与洁净车间生产要求?

- 2026-03-11代工代料模式下,如何保障PCBA交期?物料齐套与生产排程是关键

- 2026-03-11PCBA代工代料出现质量问题,责任如何界定?

- 2026-03-10电源类产品PCBA代工代料,对安规元器件与高压测试的管控要点

- 2026-03-04PCBA代工代料价格如何计算?BOM配齐、SMT贴片、测试全包报价咨询

- 1深圳SMT贴片加工如何计算报价?

- 22026年小家电行业在PCBA代工代料中应用自动化光学检测(AOI)的最新行业标准是什么?

- 3代工代料模式下,智能家居产品的高频高速信号完整性测试规范包含哪些核心指标?

- 4深圳周边一站式PCBA代工代料厂家推荐:高效率与质量的优选方案

- 5PCBA代工代料与来料加工,哪种模式综合成本更低?求真实对比

- 6医疗级PCBA代工代料,如何满足ISO13485与洁净车间生产要求?

- 7代工代料模式下,如何保障PCBA交期?物料齐套与生产排程是关键

- 8PCBA代工代料出现质量问题,责任如何界定?

- 9电源类产品PCBA代工代料,对安规元器件与高压测试的管控要点

- 10PCBA代工代料价格如何计算?BOM配齐、SMT贴片、测试全包报价咨询