HDI PCB设计中的阻抗匹配

- 发表时间:2021-04-07 10:57:26

- 来源:HDI PCB设计

- 人气:830

阻抗匹配

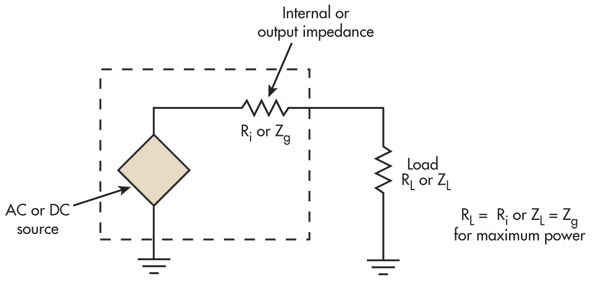

阻抗匹配意味着在传输源时,负载阻抗必须等于传输线的特征阻抗。在这种情况下,传输将不会反射,这表明所有源均已被负载吸收。相反,在传输过程中存在源损失。在HDI PCB设计中,阻抗匹配与信号质量有关。

PCB走线何时需要阻抗匹配?

它不是主要由频率决定,而是关键是信号的陡度,即信号的上升/下降时间。通常认为,如果信号的上升/下降时间(基于10%到90%)小于线延迟的6倍,则它是高速信号,必须注意阻抗匹配。导线延迟通常设置为150ps /英寸。

特性阻抗

在信号沿传输线传播期间,如果传输线上到处都有一致的信号传播速度,并且每单位长度的电容相同,则信号在传播过程中始终会看到完全一致的瞬时阻抗。由于阻抗在整个传输线中保持恒定,因此我们使用特定名称来表示该特性或特定传输线的特性,这被称为传输线的特性阻抗。特性阻抗是指沿传输线看到信号时的瞬时阻抗值。特性阻抗与PCB引线所在的板层,PCB使用的材料(介电常数),走线宽度,以及导体与焊盘之间的距离,与走线长度无关。可以使用软件来计算特征阻抗。在HDI PCB设计中,数字信号的走线阻抗通常设计为50欧姆,这是一个近似值。通常,同轴电缆的基带为50欧姆,频带为75欧姆,双绞线(差分)为100欧姆。

阻抗匹配的常用方法?

串联匹配

在信号源的阻抗低于传输线的特征阻抗的条件下,在信号源和传输线之间串联电阻R,使得信号源的输出阻抗与信号源的特征阻抗匹配。传输线,从负载反射的信号是为了抑制第二次反射的发生。

匹配电阻选择原理:匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗。普通CMOS和TTL驱动器的输出阻抗将随信号电平而变化。因此,对于TTL或CMOS电路,不可能有一个非常正确的匹配电阻,只能考虑一个折衷方案。具有链形拓扑的信号网络不适合串联终端。所有负载必须连接到传输线的末端。

串联终端匹配是最常用的。它的优点是功耗低,驱动器没有额外的直流负载,信号与地之间没有额外的阻抗,并且仅需要一个电阻性元件。

常见应用:通用CMOS和TTL电路的阻抗匹配。USB信号也以这种方式采样以进行阻抗匹配。

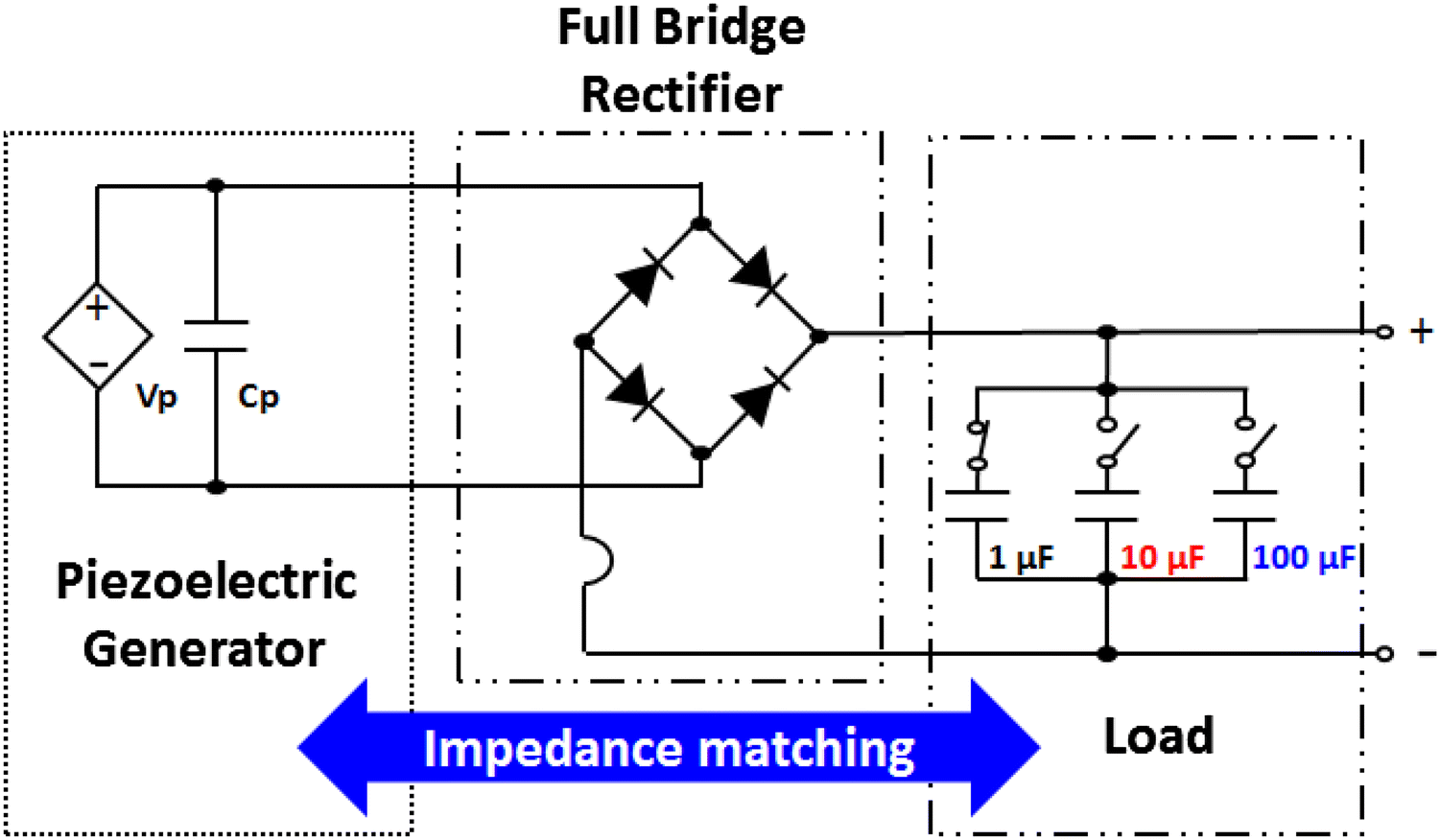

并联端子匹配

在信号源的阻抗非常小的情况下,通过增加并联电阻以消除负载端的反射,可以使负载端的输入阻抗与传输线的特性阻抗匹配。实现形式分为单电阻和双电阻两种形式。

匹配电阻选择原理:当芯片的输入阻抗很高时,对于单电阻类型,负载端的并联电阻值必须接近或等于传输线的特性阻抗;对于双电阻型,每个并联电阻值是传输线特征阻抗的两倍。

并联端子匹配的优点是简单易行,明显的缺点是会带来直流功耗:单电阻方法的直流功耗与信号的占空比密切相关;不论信号高还是低,双电阻方法都具有直流功耗,但电流比单电阻方法小一半。

常见应用:大多数具有高速信号的应用。

1.SSTL驱动程序,例如DDR,DDR2。它采用单电阻形式,并与VTT(通常为IOVDD的一半)并联。DDR2数据信号的并行匹配电阻内置在芯片中。

2.高速串行数据接口,如TMDS。它采用单电阻形式,在接收设备处与IOVDD并联,单端阻抗为50欧姆(差分对之间为100欧姆)。

【上一篇:】PCB制板、材质利用

【下一篇:】三种类型的开关电源缓冲电路

- 2025-02-20深圳SMT贴片加工如何计算报价?

- 2026-05-07深圳PCBA加工优选指南:5家具备IATF 16949资质的源头工厂深度盘点

- 2026-04-29如何在代工合同中界定因元器件市场波动导致的PCBA成本调整机制?

- 2026-04-29全国范围内,哪些产业带的PCBA代工代料服务在新能源充电桩领域最具集群优势?

- 2026-04-282026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 2026-04-28深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 2026-04-28润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 2026-04-24在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 2026-04-24SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 2026-04-24PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别

- 1深圳SMT贴片加工如何计算报价?

- 2深圳PCBA加工优选指南:5家具备IATF 16949资质的源头工厂深度盘点

- 3如何在代工合同中界定因元器件市场波动导致的PCBA成本调整机制?

- 4全国范围内,哪些产业带的PCBA代工代料服务在新能源充电桩领域最具集群优势?

- 52026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 6深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 7润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 8在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 9SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 10PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别