如何限制 PCB 传输线中的阻抗不连续性和信号反射

- 发表时间:2021-06-21 16:04:51

- 来源:本站

- 人气:1083

我们之前在PCB 传输线文章中快速讨论了信号反射。这是一篇关于PCB设计人员应该掌握的非常重要的主题的深入文章。首先要记住的是,由于阻抗不连续,PCB 传输线中会发生信号反射。

传输线应具有均匀的特性阻抗。阻抗的任何变化或不连续都会导致信号反射和失真。

这种现象同样适用于 PCB 走线和传输线。原因是高频信号的物理波长非常短。因此,PCB 走线表现出相同的特性。频率越高,波长越短。您甚至必须像传输线一样对待较短的走线。

信号轨迹不连续性或非均匀不连续性形成信号完整性不连续性。为了避免源端和目标端的信号失真,您必须将 PCB 走线阻抗与源端匹配。然后您必须在源端和目标端加载阻抗。这提出了一个相当大的挑战,需要仔细的 PCB 设计来减轻由阻抗不连续引起的信号衰减的影响。特性阻抗的不连续性越大,信号反射就越高。这意味着信号失真也更高。因此,尽量保持阻抗不连续性尽可能小。在幅度和时间方面。阅读:为什么受控阻抗真的很重要。

阻抗不连续性影响信号完整性

理论上,数字信号是在很短的时间内切换的方波脉冲。自然而然地,高频数字电路所需的短信号上升时间将导致与快速信号上升时间相关的极高频率。实际上,这些频率将比电路的时钟频率高一个数量级。高频数字电路的脉宽更短。从而更短的上升时间。非常短的信号上升时间意味着数字信号中包含非常高的频率。因此,高频数字信号应遵循与高频信号相关的信号完整性规则。

因此,PCB 走线阻抗的任何变化都会导致信号反射。这些会导致振铃和信号失真。这样做的结果是,在高开关频率下,阻抗不连续性对数字信号造成的失真非常严重,可能会出现信号采样错误。您可以通过以下参数表征由 PCB 走线形成的传输线:电阻、电导和走线电阻。阅读PCB 中微带线和带状线的区别。

典型的阻抗不连续性

线路的特性阻抗是电感除以电容的平方根。这是 PCB 的合理假设,因为与其电感和电容相比,高信号频率下的走线电阻和电导可以忽略不计。

阻抗不连续是任何影响走线电感与其电容之比的因素。下面是一些典型的例子:

线路中的阻抗变化:如果线路的阻抗因任何原因发生变化,例如由于铜截面的变化或走线路径的变化,互感会发生变化,并且会出现阻抗不连续。

线路中的分支:虽然可能需要将信号路由到多个设备,但分支和线路短截线的使用会改变线路阻抗,从而导致不连续。

返回信号分裂:高频信号沿着阻抗最低的路径传播,该路径位于信号走线的正下方,通常位于接地层中。返回线或接地平面中任何迫使返回信号偏离此路径的物理特征都会造成不连续性。

过孔:使用过孔将信号从 PCB 的一层传输到另一层。尽管是 PCB 设计的基本特征,但过孔的形状和尺寸会改变走线的电感和电容,从而产生另一个不连续性。要了解更多信息,请阅读如何减少 PCB 布局中的寄生电容。

如何限制阻抗不连续的影响

控制阻抗不连续性负面影响的关键是将所有 PCB 信号走线视为传输线。您应该确保信号路径上所有点的特征阻抗都相同。

确保您遵循以下准则:

匹配源阻抗和负载阻抗:确保源阻抗和负载阻抗与走线阻抗相同。您可以通过使用串联或并联电阻来实现正确的阻抗来实现这一点。此外,您必须使用正确值的电阻器终止任何开路走线。

避免分支:如果信号必须由多个芯片共享,请以菊花链方式连接线路,而不是使用分支。或者,可以使用匹配的缓冲设备将信号传输到分支。

信号返回路径:确保信号返回遵循与信号线相同的路径。如果使用接地层,请确保没有中断返回信号路径的分裂。确保走线下方有一个贯穿整个长度的实心平面,没有裂口或切口。如果没有实心平面,请使用较粗的返回走线,它应覆盖走线纵向和电介质高度的三倍。

过孔设计:将高频走线布置在尽可能远的一层上。如果需要过孔,请使用微孔代替传统的过孔。由于通孔具有显着不同的电容和电感特性,因此尽量减少它们在信号走线上的使用。在需要的地方,使用电容和电感比标准过孔小得多的微过孔。微孔还有助于使存根长度尽可能短。另一种方法是使用高密度互连或HDI PCB技术。

阻抗不连续的不利影响是严重的。您不能在以高时钟频率运行的数字 PCB 电路中忽略它们。在通过遵循合理的设计实践并在可能的情况下使用高级 PCB 设计软件来评估和减少阻抗不连续性来控制这些影响时,您应该小心。

阻抗不连续性和信号反射

均匀传输线上的信号在线路上的所有位置都会遇到恒定阻抗“Zc (V/I)”,并且信号会根据需要沿着它传输。但是,如果在任何一点存在阻抗不连续性,信号传播都会受到影响,并且信号反射会发生,就像光在其传播的介质中遇到不连续性时会发生反射一样。

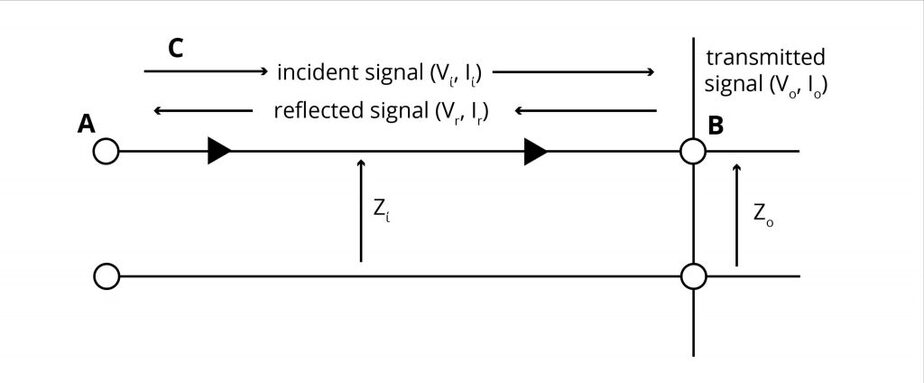

假设从 A 点到 B 点,线路是均匀的,阻抗为“Zi”;但在 B 处,存在阻抗不连续性,并且线路阻抗在 B 处及以后变为“Z0”。

假设信号从 A 在(阻抗为“Zi”的)线上向 B 发送。在 B 处,让入射信号电压和电流为“Vi”和“Ii”。那么,我们必须有:

Vi = Zi I0 (1)

现在,如果我们从线路阻抗为“Zo”的右侧看 B,那么此时 B 处的传输电压 'Vo' 和传输电流 'I0' 必须通过以下方式相关联:

V0 = Z0 I0 (2)

需要强调的是,关系式(1)和(2)是阻抗概念的基础,必须始终遵守。

给定“Vi”、“Zi”和“Zo”的值,问题是找到“Vo”的值。

情况 1:Z0 = Zi ,(即线路阻抗没有不连续性)

在这种情况下,上述方程 (1) 和 (2) 将同时满足:

V0 = Vi 和 I0 = Ii

这是可以预料的,因为在这种情况下,B 点基本上是均匀传输线上的任何点,因此在这条线上的每个 B 点,传输的信号将等于入射信号。

情况 2:Z0 ≠ Zi ,(即线路中存在阻抗不连续性)

这里,如果同时看等式(1)和(2),由于Z0≠Zi,很容易得出结论,我们不能同时有Vi=V0和Ii=I0;因为,如果我们暂时假设 Vo = Vi,那么 Ii ≠ I0;如果我们假设 Ii = I0,则 Vo ≠ Vi。因此我们得出的结论是,在阻抗不连续处,入射信号没有完全完全向前传输。

我们能够满意地解决这个问题的唯一方法是假设入射信号的一部分在阻抗不连续点 B 反射回来,并且这个反射信号叠加在入射信号上的 B 点和左边的一条线上其中;在 B 点,入射信号和叠加反射信号的结果将等于 B 点的透射信号。

因此,假设 (Vi,Ii) 的一部分在 B 点反射回“Zi”传输线。让我们用 (Vr,Ir) 表示 B 点反射信号的电压和电流。

因此,在 B 点,由于入射电压 Vi 和反射电压 Vr 产生的信号电压将为 (Vi + Vr),并且根据在 B 点应用的基尔霍夫定律,这必须等于“Vo”:

V0 = Vi + Vr (3)

由于入射电流“Ii”和反射电流“Ir”(与入射电流方向相反)叠加而产生的电流将为(Ii – Ir),并且根据应用的基尔霍夫定律在 B 点,这必须等于 'Io':

I0 = Ii – Ir (4)

反射 (Vr,Ir) 信号在阻抗为“Zi”的线路上传播,我们必须有:

Vr = Zi Ir (5)

使用等式(3)中的等式(1)、(2)和(5),我们有:

Z0I0 = ZiIi + ZiIr = (Ii + Ir)

因为,根据 (4),I0 = (Ii – Ir),我们有:

Z0 (Ii – Ir) = Zi (Ii + Ir)

或 Ii (Z0 – Zi) = Ir (Z0 + Zi)

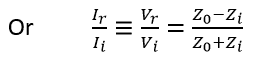

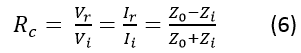

Vr/Vi 或 Ir/Ii 表示在阻抗不连续点 B 反射回来的入射信号的分数,称为反射系数“Rc”:

就“Rc”而言,B 点传输的信号电压和电流由下式给出:

Vo = Vi + Vr = (1 + Rc) x Vi (7)

并且: Io = Ii – Ir = ( 1 – Rc) x Ii (8)

由上可知,反射系数'Rc'的值取决于'Zi'和'Zo'的相对值;它们之间的差异越大,反射量就越大。可以肯定地得出结论,在阻抗为纯电阻的情况下,“Rc”值的范围可以由下式给出:

-1 ≤ Rc ≤ 1

如果 Z0 > Zi,则部分正信号被反射回来,导致脉冲信号中 B 处的电压过冲。如果 Z0 < Zi,则部分负信号被反射回来,导致脉冲信号中 B 处的电压下冲。

我们现在可以讨论“Zi”和“Zo”的相对大小的一些特殊情况。

情况 (i):传输线以其阻抗终止

这里 Z0 = Zi(因为传输线在其远端 B 端接阻抗值为“Zi”),这导致: Rc = 0 即没有反射,入射信号将完全传输到远端 B。这个案例告诉我们如何避免传输线中的反射:只需在目的地端接一个与传输线阻抗相等的阻抗即可。

情况 (ii):传输线在远端开放

这里 Z0 = ∞(因为传输线在其远端 B 处开路),导致 Rc = 1。这意味着入射信号将被完全反射,因此 V0 = 2Vi 和 I0 = 0。这意味着叠加信号电压将是入射电压的两倍,叠加信号电流将为零,正如在开放端所预期的那样。

情况 (iii):传输线短路

此处 Z0 = 0(因为线路在远端 B 处短路),导致 Rc = -1,因此 V0 = 0 且 I0 = 2Ii。这意味着全入射信号的负值被反射回来,使短路端的电压如预期的那样为零。

情况(iv):当Zo≠Zi但差异很小时

如果“Zo”与“Zi”相差约 20%,反射系数“Rc”将为约 10%,这意味着大约 5% 的入射信号将被反射。在大多数电路设计中,由于可用的噪声容限,阻抗不匹配导致的 10% 信号失真是可以接受的。

各种类型的阻抗不连续性及其可能的原因:

由于传输线的阻抗取决于导体的几何形状和 PCB 材料特性,因此这些特性的任何变化都会导致阻抗发生变化。此处列出了一些实例:

在线路的源头或目的地/末端。源阻抗或接收器阻抗通常与线路的阻抗不同。

信号线和返回路径之间的 PCB 材料的线宽或高度(即铜厚度)的变化或高度和/或介电常数的变化。

信号走线路径中的过孔:过孔通常没有与信号走线相同的阻抗——没有多少设计人员试图找出过孔是什么阻抗是。优点是过孔长度很小,所以它的效果会以光点的形式出现。过孔的开始将引入一个反射,然后过孔的末端将引入另一个反射。如果过孔阻抗小于线路阻抗,这将导致信号电压出现小幅下冲。对于非常高速的信号,过孔阻抗不连续性确实很重要,建议设计人员在关键信号线中避免它们,如有必要,避免在线中间——而是将它们靠近源和/或目标,以便它们可以与源和目标阻抗不连续一起处理。

如果信号线分支到多个目的地,在分支点,我们会看到阻抗不连续。如果信号线在其路径上的不同点被抽头,则在抽头点处将存在阻抗不连续性。

多次反射:

考虑一条传输线,其长度使得其上的总传播时间为“tp”,并使其阻抗为 50 欧姆。在源端,它连接到一个阻抗为 16.67 欧姆的源,在目的地,它连接到一个 150 欧姆的负载。因此,源处的反射百分比将为 -50%,而在负载时为 +50%。

由源发射的 1V 信号将在时间 0 在线路上降低到 1V x 50/(16.67+50)= 0.75V。在时间“tp”,这个 0.75V 信号将到达目的地,即 50%,即 0。 375V 将被反射回来,使负载电压 = 1.5×0.75 = 1.125V。现在,0.375V 反射信号将在时间“2tp”到达源,其中 -50% 即 -0.1875V 信号将反射到负载。这将在时间 '3tp' 到达负载,其中 50% = -0.0938V 将被反映,因此将 -0.1875-0.0938 = -0.2813V 添加到 1.125V 的旧负载电压,使其现在 = 0.8438V。

同时,-0.0938V的反射信号将在时间'4tp'到达源,其中-50% = +0.04688V将被反射到负载;这将在“5tp”到达负载,其中 +50% = +0.02345V 将被反射回来,因此将 +0.04688V +0.02344V = + 0.07032V 添加到负载,使负载电压现在 = 0.9141V。同时,强度+0.02344V的反射信号将在'6tp'时间到达源,其中-50%即-0.01172V将在'7tp'反射到达负载,其+50%将被反射回来,向负载添加 -0.01172Vx150% = -0.01758V,使负载电压现在 = 0.9141V-0.01758V= 0.8965V。等等......所以目的地的信号看起来像:

从0到tp:0V

tp到3tp:1.125V

3tp到5tp:0.8438V

5tp到7tp:0.9141V

7tp到9tp:0.8965V

因此,我们将看到目的地的信号振铃。如果源阻抗小于线路阻抗,导致源端出现负反射,而目的阻抗较高,导致目的端出现正反射,则会出现带有过冲和下冲的振铃。

【上一篇:】PCB刚柔结合降低电子产品组装成本

【下一篇:】如何降低PCB布局中的寄生电容

- 2025-02-20深圳SMT贴片加工如何计算报价?

- 2026-04-282026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 2026-04-28深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 2026-04-28润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 2026-04-24在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 2026-04-24SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 2026-04-24PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别

- 2026-04-23智能玩具PCBA代工:选“专注SMT专精厂”还是“带组装的OEM厂”更划算?

- 2026-04-23深圳市润泽五洲电子科技有限公司在PCBA一站式服务方面的市场口碑和交付稳定性如何?

- 2026-04-23什么是IATF 16949质量管理体系?深度解析汽车电子PCBA制程管控的硬性要求

- 1深圳SMT贴片加工如何计算报价?

- 22026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 3深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 4润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 5在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 6SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 7PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别

- 8智能玩具PCBA代工:选“专注SMT专精厂”还是“带组装的OEM厂”更划算?

- 9深圳市润泽五洲电子科技有限公司在PCBA一站式服务方面的市场口碑和交付稳定性如何?

- 10什么是IATF 16949质量管理体系?深度解析汽车电子PCBA制程管控的硬性要求