如何降低PCB布局中的寄生电容

- 发表时间:2021-06-18 16:08:47

- 来源:本站

- 人气:961

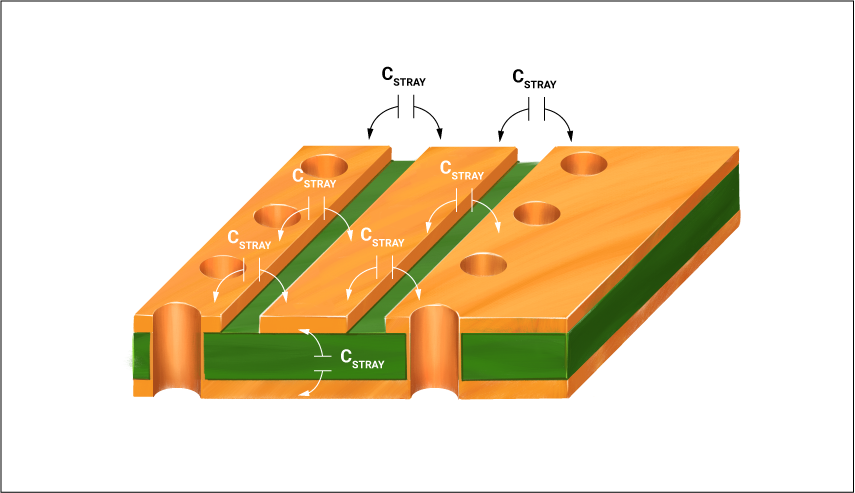

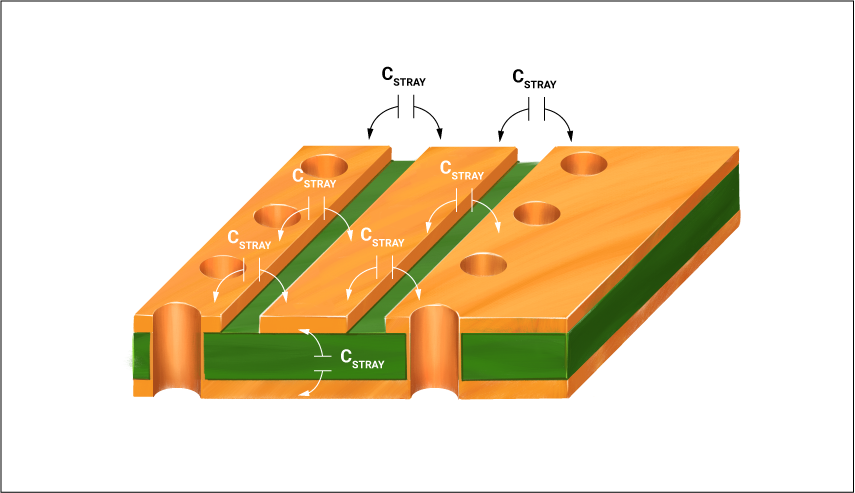

PCB 由多个平行跨接的导体组成,例如走线,由绝缘体隔开。这些走线与介电材料一起形成一个电容器,从而导致不需要的寄生电容或杂散电容效应。

PCB 中的寄生元件可能是寄生电容、寄生电阻和寄生电感。当走线靠近时,寄生电容效应在高频板中尤为突出。这种效果是完全不需要的,会影响设备的功能。它会导致串扰、EMI和信号完整性等问题。处理高频、高数据速率和混合信号板的 PCB 设计人员在设计 PCB 布局时必须考虑寄生电容和电感效应。

在以下部分中,我们将了解寄生电容的定义及其对我们电路板的影响。

PCB中的寄生电容是什么?

紧密放置的 PCB 导体形成一个虚拟电容器,从而产生寄生电容效应。

寄生电容或杂散电容是由电介质隔开的两条迹线之间形成的虚拟电容器的结果。它是由于载流走线靠近时产生的电位差而发生的。要了解更多信息,请阅读线路电流容量在 PCB 设计中的作用。

如果导体适当绝缘,这种效果甚至是可能的。由于没有理想的电路,因此无法避免寄生电容。

如何计算寄生电容?

电容器中的充电放电循环。

寄生电容是导体的固有特性。它是每单位电位变化的存储量。寄生电容的计算公式为 C= q/v。其中 C 是以法拉为单位的电容,v 是以伏特为单位的电压,q 是以库仑为单位的电荷。

对于不随时间变化的恒定电信号,dv/dt = 0,这意味着电位没有变化;因此 i = 0。

如果电路回路中有电容,dv/dt会收敛到一个固定值,即电位变化,产生电流;因此 i≠0。

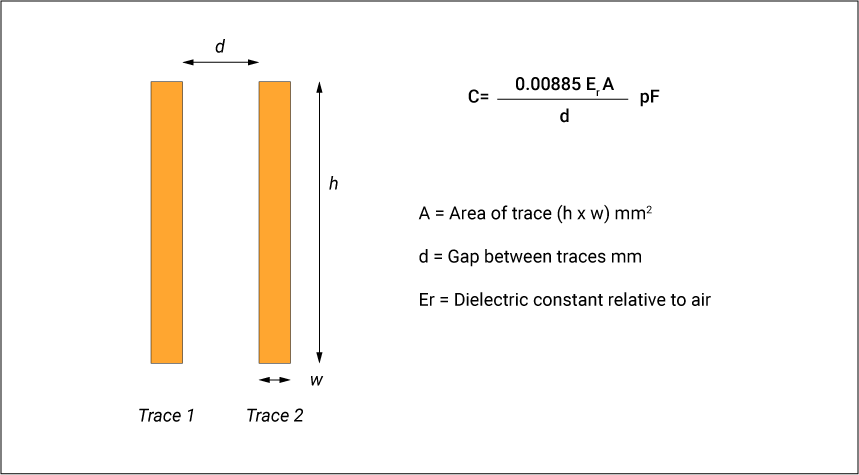

走线电容计算

平行板电容器的电容由 C= (kA/11.3d)pF 给出。其中 C 是电容,A 是以 cm 2为单位的极板面积,k 是板材料的相对介电常数,d 是极板之间的距离,单位为 cm。

走线电容计算

什么是寄生电容效应?

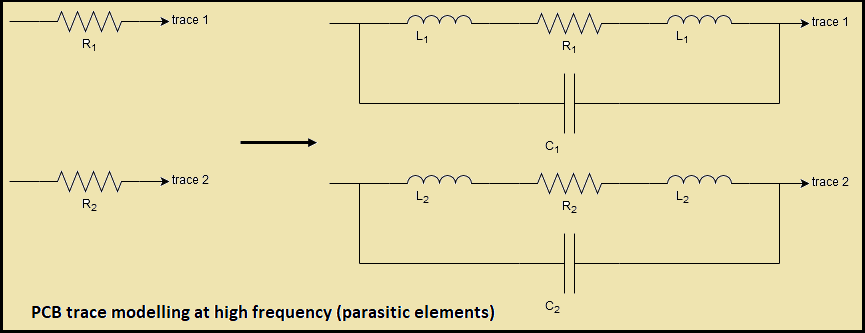

高频下的 PCB 寄生元件建模。

寄生电容效应是高频电路板中的一个问题。在低频运行时,寄生元件可以忽略不计,因为它们不会真正影响系统功能。电路板上的每个焊盘都有其寄生电容,每条走线都有寄生电感。焊盘还增加了寄生电阻,从而刺激了 IR 损失。寄生电容可能存在于 PCB、裸板、PCBA、组装板以及元件封装内的导体之间,尤其是表面贴装器件(SMD)。

由于本征电容器极板具有电位差,因此存在电流流动的机会。电荷是否存储在电容器极板之间并不重要;电流不会流动,直到有电位差。一旦该电位差增加,对于对信号完整性产生负面影响的所需信号路径,可以观察到流向负载的电子流的相应减少。

杂散电容和寄生电容的区别?

术语杂散电容通常与寄生电容互换使用。然而,寄生电容说明它会妨碍电路操作,而杂散电容说明如何引入不需要的电容。

什么是杂散电容?

由于两个 PCB 导体之间形成的虚拟电容,而且由于周围环境的影响,杂散电容并不总是会被感应到。因此,它被称为杂散电容。

PCB中的寄生电阻是什么?

寄生电阻沿着走线串联或作为导电元件之间的分流器存在。

PCB中的寄生电感是什么?

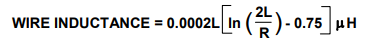

寄生电感沿着走线存在,表现出存储和耗散电能的行为,就像实际的电感器一样。所有导体都是电感性的,在高频下,即使是相对较短的导线或 PCB 走线的电感也可能很重要。

其中 R 是导线半径,L 是长度。

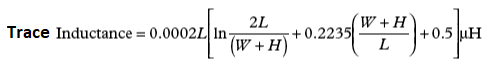

如何找到PCB走线的电感?

走线电感随着走线长度和缺少接地层而增加。

其中 W 是走线宽度,L 是走线长度,H 是走线厚度。

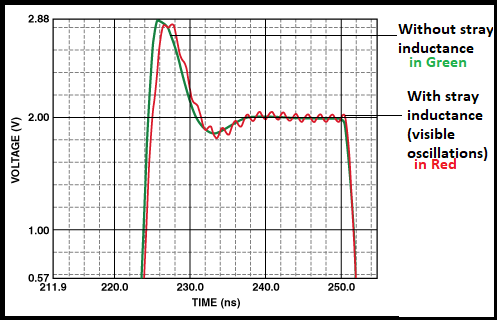

例如,高速运算放大器同相输入端的 2.54cm 走线将产生 29nH 的杂散电感。这足以启动低级振荡。使用接地层可以减轻杂散电感。

杂散电感会导致运算放大器输出的低电平振荡。图表来源:ADI

什么导致寄生电容?

在高频下,电路板中的电流受到寄生电容的影响。因为当频率增加时,电容器往往会变成导体。请注意,当频率增加时,电容器将充当值非常小的电阻器(接近短路),导致电流过大。

Z c = 1/ 2πf c;f c = 1/ ω c因此,随着频率的增加,Z c也增加。

寄生电容会在高频操作期间让您发冷,因为电容器在无限频率下就像一根电线。这就是为什么它会意外地将任何 PCB 的参考平面连接到机箱的原因。

寄生电容效应可能是串扰和噪声、来自输出的不良反馈以及谐振电路的形成。因此,必须注意整体PCB 设计,特别是布局。在将导电体放置在另一个导电体旁边时,良好的布局应格外小心。

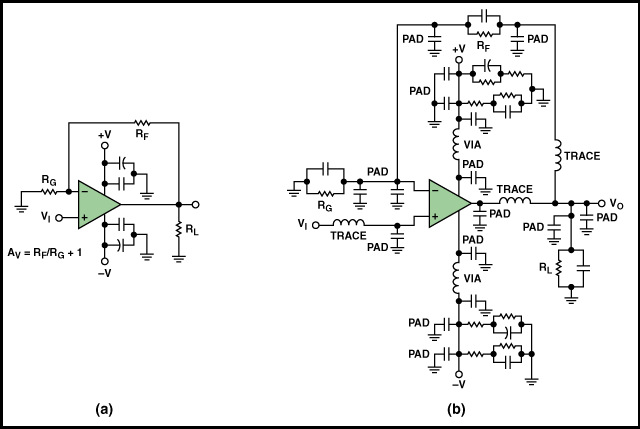

寄生元件包括由封装引线、长走线、焊盘到地、焊盘到电源平面和焊盘到走线电容器形成的电感,包括与通孔的相互作用等。将寄生元件理解为寄生元件,对您的电路性能构成威胁。不想要的和不可避免的,但同时是可控的。

让我们以同相运算放大器的典型原理图为例(图 a)。检查带有寄生元素的图 b:

带有寄生元件的同相运算放大器的示意图。图片来源:ADI

要了解有关原理图符号和原理图的更多信息,请阅读我们的文章原理图的含义是什么?

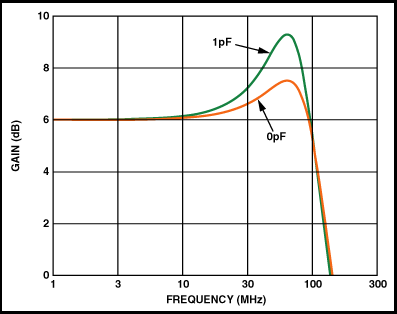

在高速电路中,十分之几皮法就足以影响电路性能。例如,反相输入端的 1pF 寄生电容会导致频域中出现 2dB 的峰值。如果超过 1pF,就会引起不稳定和振荡。

反相运算放大器输入端的寄生电容。图片来源:ADI

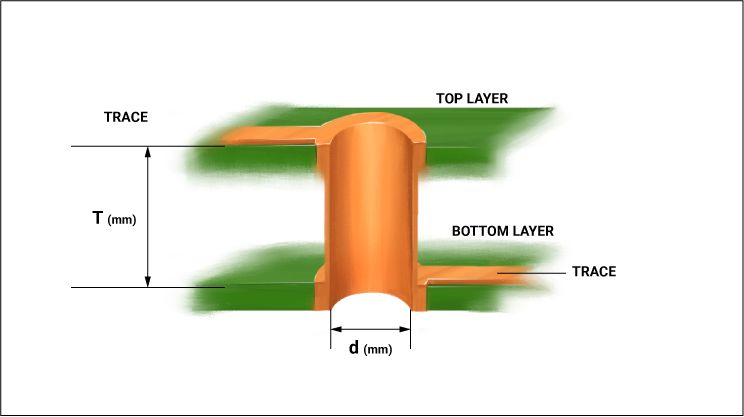

通孔也充当寄生元件。它们引入了电容和电感。

过孔会引入电容和电感。

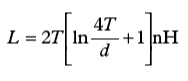

过孔的寄生电感由下式给出:

其中 T 是电介质的厚度,d 是通孔的直径(cms)。

过孔的寄生电容由下式给出:

其中 εr 是板材料的相对磁导率,T 是板的厚度,D1 是过孔周围焊盘的直径,D2 是地平面中间隙孔的直径。阅读我们关于如何选择用于制造的 PCB 材料和层压板的文章。

请记住,电感通孔与寄生电容相结合可以形成谐振电路。通孔的自感足够小,这些谐振在 GHz 范围内,但电感器串联添加,降低了谐振频率。不要在高速电路的关键走线上放置多个过孔。另一个问题是过孔会在地平面上形成孔洞,从而形成接地回路。应该避免它们。最好的模拟布局必须在 PCB 的顶层布线所有信号走线。阅读11 种最佳高速 PCB 布线实践。

减少 PCB 布局中的寄生电容

电容器阻止低频和直流信号并通过电子电路中的高频信号。电容器通过高频信号的这种特性(电容器放电的速度是它们被用来代替速度慢得多的电池的另一个原因)是造成高速电路中杂散电容问题的原因。对于导体,杂散电容会引入EMI或噪声,它们会沿着电线和电缆传播或转移到附近的相邻迹线。通常,消除杂散电容是不可能的。尽管如此,还是有一些有效的方法可以在 PCB 布局级别上缓解这种情况。

避免平行走线:平行走线时,两种金属之间存在最大面积,因此它们之间存在最大电容。

Moating:电源层被视为交流接地,其行为与接地层完全相同。因此,去除电源层与去除导体附近的接地层一样重要。这种技术称为护城河。

使用法拉第屏蔽或保护环:法拉第屏蔽充当屏蔽板,将其放置在两条迹线之间以最小化电容效应。

增加相邻走线之间的空间:电容随距离减小。使用2W或3W规则。

避免过度使用过孔:过孔是连接 PCB 各层所必需的。但它们的过度使用会增加电容。为了减少 PTH 耦合,最好在没有连接的层上减少通孔周围的环形环。因此,最大限度地减少来自组件(如 BGA)的过孔数量。

仔细分离组件: 仔细分离组件和电线、保护环、电源层、接地层、输出和输入之间的屏蔽以及传输线的正确端接对于减少不需要的寄生电容至关重要。

使用低介电常数介电材料: 保持所有其他变量不变,介电材料的介电常数越高,杂散电容越大,而介电常数越小,杂散电容越小。

信号层应该夹在两个地平面之间,或者夹在一个地平面或电源平面之间:在4层板中,您可以将电源平面放在底层,并在电源平面和地平面之间布置一些敏感的走线。这将防止来自一层信号的 EMI 引起另一层信号中的噪声。

确定合适的层厚:较薄的层会减少环路面积和寄生电感,但会增加寄生电容。您可以使用具有不同层堆栈的模拟工具来确定正确的层厚度。

阻抗匹配:在高速数字应用中,多条数据线以数十 Gbps 的速度运行,由于寄生电容和电感导致阻抗不匹配。寄生引起的任何不匹配都会在线路上的某处产生反射,最终增加时序抖动和误码率。阻抗应该在传输高速数据的信号线上匹配。有关详细说明,请阅读如何限制 PCB 传输线中的阻抗不连续性和信号反射。

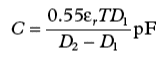

使用 TDR 测量寄生电容

当有几个易于使用的出色分辨率 LCR 表可用时,使用时域反射计 (TDR) 测量电感或电容有什么意义?答案是TDR支持对电路中存在的器件和结构进行测量。在测量寄生元件时,设备周围的环境可能会影响要测量的数量。对于有效测量,对电路中存在的器件进行测量至关重要。

TDR测试框图

此外,在测量包含传输线的系统中的设备或结构的影响时,TDR 允许单独测量传输线特性和设备特性,而无需物理分离电路中的任何内容。请允许我们解释 TDR 如何测量用 LCR 表难以测量的量。

示例:让我们以在接地平面上具有长而窄走线的 PCB为例,形成一条微带线。在某些时候,走线通过过孔从 PCB 的顶部延伸到底部,依此类推。只要过孔穿过地平面,它就会有一个小开口。现在,假设通孔增加了接地电容。在这里,它是顶部和底部传输线之间接地的分立电容。我们假设传输线的特性,我们需要测量两条传输线之间的对地电容。

另请阅读我们的文章电路仿真如何工作?

LCR 表测量走线通路结构和地之间的总电容。但是不能分别测量过孔电容和走线电容。对于单独的电容测量,从板上移除走线。通过这种方式,可以测量过孔和地之间的电容。很明显,这个电容值不能被认为对模型是正确的,因为不包括迹线。

另一方面,TDR 在 PCB 走线上发射阶跃波并观察从通孔不连续处反射的波形。通过对反射波形进行积分和缩放,可以计算出由过孔引起的“过量”电容量。此方法为模型提供正确的电容值。

两次测量之间存在不匹配,因为 LCR 表测量的是通孔的总电容,而 TDR 测量的是通孔的多余电容。如果过孔的串联电感为零,则其总电容将被视为与其超额电容相同。由于过孔的串联电感不为零,因此必须考虑过孔的完整模型,包括串联电感和并联电容。考虑到过孔是电容性的,现在可以通过消除串联电感并仅包括多余电容来代替总电容来简化模型。使用 TDR 测量的多余电容是模型的正确值。首先对走线-过孔-走线结构进行建模,以预测过孔对沿走线传播的信号的影响。TDR 沿迹线传播输入脉冲以进行测量。通过这种方式,TDR 提供了对未知量的直接测量。

不幸的是,不可能完全消除寄生元件。但是,您可以选择一些简单的 PCB 布局来减少寄生电容效应。选择正确的组件还可以防止寄生电容和电感引起的信号问题。准确的设计和制造决策可以控制这些寄生效应。

【上一篇:】如何限制 PCB 传输线中的阻抗不连续性和信号反射

【下一篇:】如何处理电流返回路径以获得更好的信号完整性

- 2025-02-20深圳SMT贴片加工如何计算报价?

- 2026-04-29如何在代工合同中界定因元器件市场波动导致的PCBA成本调整机制?

- 2026-04-29全国范围内,哪些产业带的PCBA代工代料服务在新能源充电桩领域最具集群优势?

- 2026-04-282026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 2026-04-28深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 2026-04-28润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 2026-04-24在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 2026-04-24SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 2026-04-24PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别

- 2026-04-23智能玩具PCBA代工:选“专注SMT专精厂”还是“带组装的OEM厂”更划算?

- 1深圳SMT贴片加工如何计算报价?

- 2如何在代工合同中界定因元器件市场波动导致的PCBA成本调整机制?

- 3全国范围内,哪些产业带的PCBA代工代料服务在新能源充电桩领域最具集群优势?

- 42026年PCBA加工行业中,衡量“一站式服务”质量的关键技术参数有哪些?

- 5深圳地区5家具备IATF 16949认证且擅长新能源充电桩PCBA加工的优质供应商名单

- 6润泽五洲电子科技是否具备处理复杂BGA封装和异形插件的DIP焊接工艺能力?

- 7在东莞和深圳地区,哪家PCBA工厂在新能源充电桩领域的整机组装经验最丰富?

- 8SMT贴片加工中的“红胶工艺”与“锡膏工艺”解析:在波峰焊环节的不同应用

- 9PCBA加工中的“代料代工”模式解析:与传统来料加工的责任界定区别

- 10智能玩具PCBA代工:选“专注SMT专精厂”还是“带组装的OEM厂”更划算?